Intel展示3D堆叠CMOS晶体管技术

发布时间:2023-12-12 13:44:00 阅读量:1081

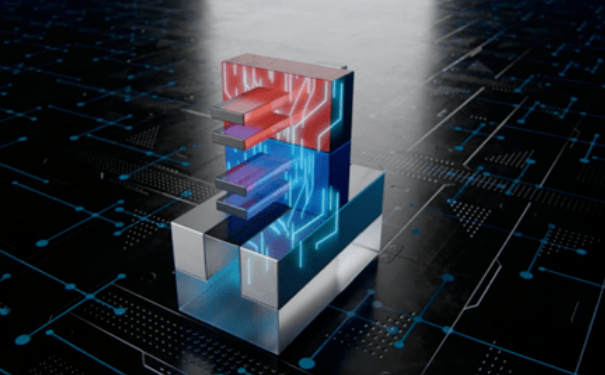

近日,在今年的IEEE国际电子器件会议(IEDM 2023)上,英特尔向外界展示了其在半导体技术方面的多项突破性成果。其中,3D堆叠CMOS(互补金属氧化物半导体)晶体管的研发成为焦点。

一是3D堆叠CMOS晶体管,一种栅极间距垂直堆叠互补场效应晶体管(CFET),结合了背面供电(PowerVia)、直接背面触点(direct backside contact),可以缩微至60nm。

它可以通过晶体管堆叠提升面积效率和性能优势,显现了Intel在GAA全环绕栅极晶体管领域的领先地位。

其中,PwoerVia技术将于2024年在Intel 20A节点上做好投产准备。

二是同一块300毫米晶圆上集成硅晶体管、氮化镓晶体管,且性能良好。

这为实现300毫米硅基氮化镓(GaN-on-silicon)晶圆开辟一条可行的路径。

今年,Intel在硅和氮化镓集成方面取得突破性进展,成功实现了高性能、大规模的集成电路供电方案,名为“DrGaN”。

三是全新的过渡金属二硫属化物(TMD)晶体管,可以让晶体管物理栅极长度微缩到10纳米以下。

除了这种新的2D通道材料,Intel还展示了率先实现的两项相关技术:GAA 2D过渡金属二硫属化物PMOS晶体管,以及300毫米晶圆上制造的2D PMOS晶体管。

英特尔高级副总裁兼组件研究部总经理 Sanjay Natarajan 表示,“随着我们进入 Angstrom 时代以及确定四年五个节点的目标,持续创新已经变得比以往任何时候都关键。在 IEDM 2023 上,英特尔展示了其在推动摩尔定律的研究进展方面所取得的进展,强调了我们为下一代移动计算提供进一步扩展和高效供电的能力。”

标签: 晶体管 Intel

郑重声明:本文版权归原作者所有,转载文章仅为传播更多信息之目的,如作者信息标记有误,请第一时间联系我们修改或删除,感谢您的关注!

购物指南

购物指南 消费保障

消费保障 关于我们

关于我们